Percobaan 1 kondisi 7

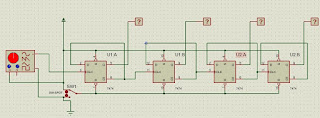

Buatlah rangkaian seperti gambar percobaan 1 dengan menggunakan D flip flop dan output 4 bit

[kembali]

2. Gambar Rangkaian Simulasi

Rangkaian sebelum dijalankan

Rangkaian setelah dijalankan (logic probe akan berubah secara berurutan)

[kembali]

3. Video Simulasi

[kembali]

4. Prinsip Kerja Rangkaian

Pada rangkaian counter ini adalah counter asynchrous, dimana

transisi clocknya terjadi secara berurutan. Pada awalnya imput berupa sinyal

pulsa yang bisa berlogika 1 dan 0 masuk ke clock pada flip flop pertama yang

akan masuk ke input data D. Pada input data D terdapat gerbang NOT yang

merupakan bentuk penyempurnaan dari RS flip flop agar tidak terjadi kondisi

terlarang (tidak tentu). Selanjutnya output drai Q dan Q’ tergantung inputan

pada clock maupun data D.

Sinyal pulsa hanya terhubung pada flip flop pertama, maka

flip flop kedua harus menunggu nilai logika dari flip flop pertama. Pada

kondisi tersebut maka logic probe pada rangkaian akan menampilkan nilai secara

berurutan tergantung drai nilai logika pada pin Q.

Pada saat input bernilai 1 maka logic probe pertama akan

menampilkan angka 1, saat input bernilai 0, maka logic probe pertama meampilkan

angka 0 dan logic probe kedua akan menampilkan angka 1. Nah ini telah terjadi

register (perpindahan). Dan pada saat input kembali masuk dari flip flop pertama,

maka logic probe kedua akan menampilkan angka 1 sementara (delay) dan ketika

input terus masuk, input berangsur-angsur berpindah sampai ke flip flop

terakhir (logic probe ke empat akan menampilkan angka 1). Lalu output akan

keluar secara bersama. Maksimalnya sampai semua logic probe menampilkan output

angka 1 yaitu 1111. Output dikendalikan oleh sinyal kontrol dari flip flop

pertama. Apabila saklar dihubungkan ke ground maka semua logic probe akan

menampilkan angka 0 secara serentak yaitu 0000.

[kembali]

[kembali]

5. Link Download

Download Video Simulasi [ DOWNLOAD ]

Download HTML [ DOWNLOAD ]

[kembali]

Tidak ada komentar:

Posting Komentar